依照客户提供的失效信息,与客户讨论后给出的最终方案如下表。

1.零件本体是否有损伤

2.器件表面丝印核对

NO

检测项目

目的

设备

1

外观检测

3D显微镜

2

电性量测(IV曲线)

通过IV曲线确定产品功能问题

特性曲线仪

3

化学开封

内部芯片是否损伤

激光开封机+化学开封

4

OBIRCH测试

内部芯片损伤位置定位

OBIRCH侦测仪

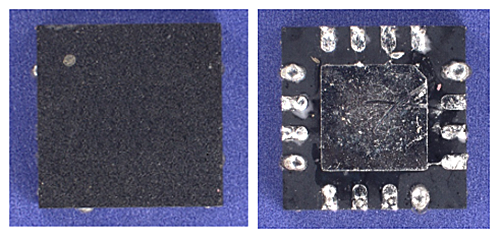

3.1 外观检查

产品整体结构正常,正表面丝印清晰可识别,背面焊盘有焊锡残留,没有发现有机械裂痕及烧伤痕迹。

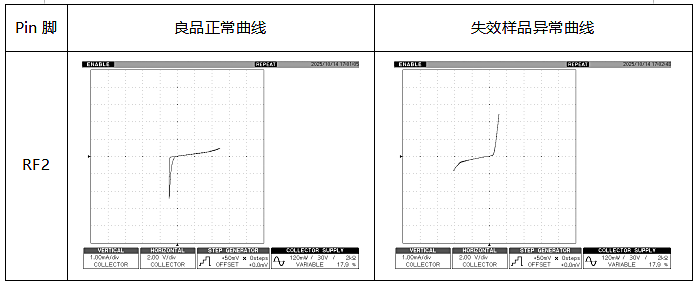

3.2 IV量测

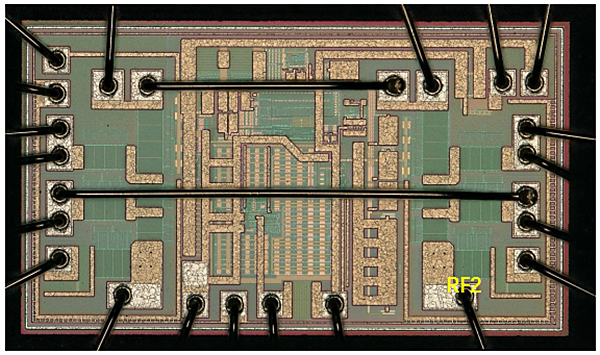

依照产品Pin脚结构图(如下图),对产品所有功能Pin进行IV信号量测,并与良品进行比对,其中发现RF2功能pin对地漏电明显。

产品Pin脚结构图

3.3 开封测试对失效样品通过激光打磨及化学腐蚀,观察内部晶圆,绑线保留完整,晶圆表面未发现异常。

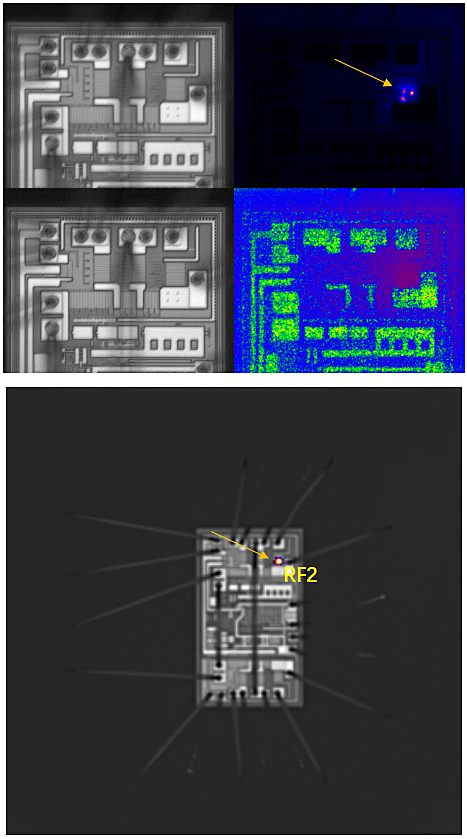

通过OBIRCH(镭射光束诱发阻抗值变化测试)测试手段,对漏电异常RF2脚进行追踪,在晶圆表面呈现异常热点。

四、结论

样品编号

结果

外观检测

样品表面未发现损伤

IV量测

与良品比对,失效样品1#“RF2-GND”IV 曲线明显有差异

开封测试

失效样品 1#芯片表面未发现有异常

OBIRCH测试

发现异常热点

综合以上测试结果:考虑失效原因是ESD损伤。

推荐阅读:

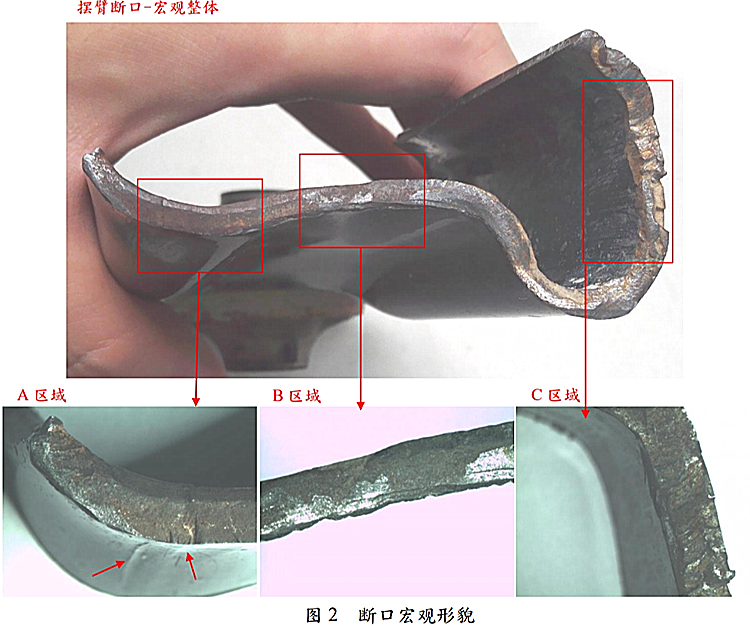

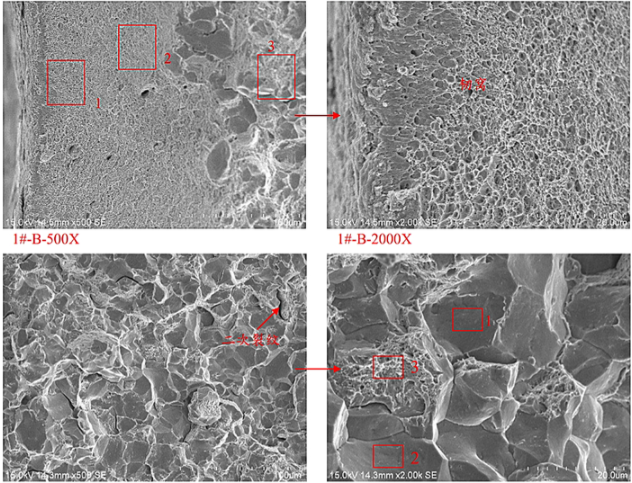

【失效分析】汽车摆臂断裂分析

2024-10-29

【失效分析】汽车摆臂断裂分析

2024-10-29

【失效分析】汽车齿轮卡圈断裂分析

2024-10-26

【失效分析】汽车齿轮卡圈断裂分析

2024-10-26

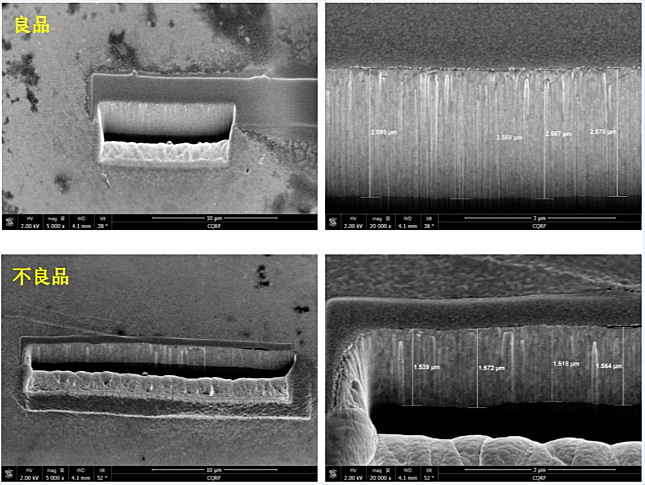

FPC钢片接地电阻偏高不良分析

2024-09-25

FPC钢片接地电阻偏高不良分析

2024-09-25

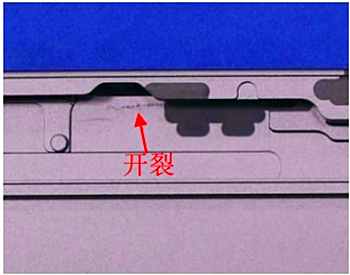

【失效分析】铝合金外壳开裂不良分析

2024-09-04

【失效分析】铝合金外壳开裂不良分析

2024-09-04

【失效分析】汽车仪表盘闪烁

2024-08-24

【失效分析】汽车仪表盘闪烁

2024-08-24

【失效分析】白光LED路灯发黄

2024-07-13

【失效分析】白光LED路灯发黄

2024-07-13